Jun 03, 2025 | 3 min read

\( \newcommand{\bra}[1]{\langle #1|} \) \( \newcommand{\ket}[1]{|#1\rangle} \) \( \newcommand{\branew}[1]{\langle #1|} \) \( \newcommand{\ketnew}[1]{\langle #1|} \) \( \newcommand{\braket}[2]{\langle #1|#2\rangle} \) \( \newcommand{\ketbra}[2]{| #1\rangle \langle #2 |} \) \( \newcommand{\i}{{\color{blue} i}} \) \( \newcommand{\Hil}{{\cal H}} \) \( \newcommand{\cg}[1]{{\rm C}#1} \) \( \newcommand{\lp}{\left(} \) \( \newcommand{\rp}{\right)} \) \( \newcommand{\lc}{\left[} \) \( \newcommand{\rc}{\right]} \) \( \newcommand{\lch}{\left\{} \) \( \newcommand{\rch}{\right\}} \) \( \newcommand{\Lp}{\Bigl(} \) \( \newcommand{\Rp}{\Bigr)} \) \( \newcommand{\Lc}{\Bigl[} \) \( \newcommand{\Rc}{\Bigr]} \) \( \newcommand{\Lch}{\Bigl\{} \) \( \newcommand{\Rch}{\Bigr\}} \) \( \newcommand{\rqa}{\quad \Rightarrow \quad} \) \( \newcommand{\bm}{\boldsymbol}\)

3.11. Conectividad.#

La conectividad es una característica importante de un procesador cuántico. Cuantos más qubits estén conectados entre sí, menos puertas SWAP habrá que ejecutar para entrelazarlos lógicamente.

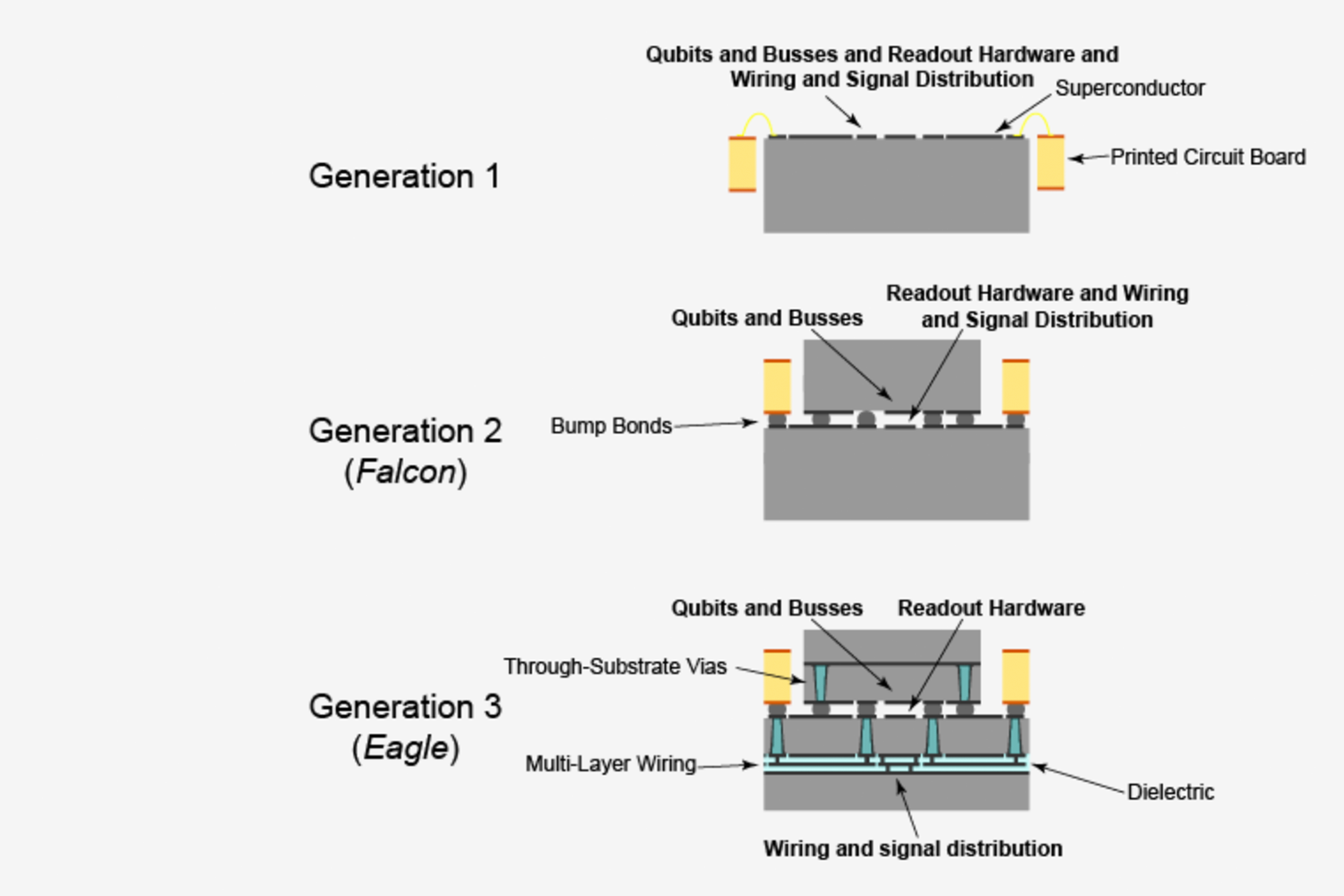

Con las estructuras 2D, uno de los problemas a resolver radica en las conexiones internas del chipset. Estas topologías consisten en una única capa de metal sobre la oblea de qubits y una placa de circuito impreso. Aunque este esquema funciona bien para topologías en anillo (aquellas en las que los qubits están dispuestos en un anillo), se rompe si hay qubits en el centro del anillo porque no hay forma forma de enviarles señales de microondas.

También tenemos la arquitectura 3D con dos capas. Esta consiste en dos chips separados, cada uno con una capa de metal estampado, unidos por uniones superconductoras: una capa para la lectura de qubits (oblea intercalada) y otra para las operaciones con qubits. Este esquema permite llevar las señales de microondas al centro del chip de qubits, “rompiendo el plano”.

Nota (Los proceadores Falcon y Hummingbird de IBM)

Esta fue la piedra angular de los procesadores como el Falcon (27 qubits) y el Hummingbird (65 qubits) de IBM. Sin embargo, según IBM: (esta topología) requería que todas las líneas de control y lectura de los qubits se dirigieran a la periferia del chip, y que las capas metálicas no estuvieran aisladas entre sí.

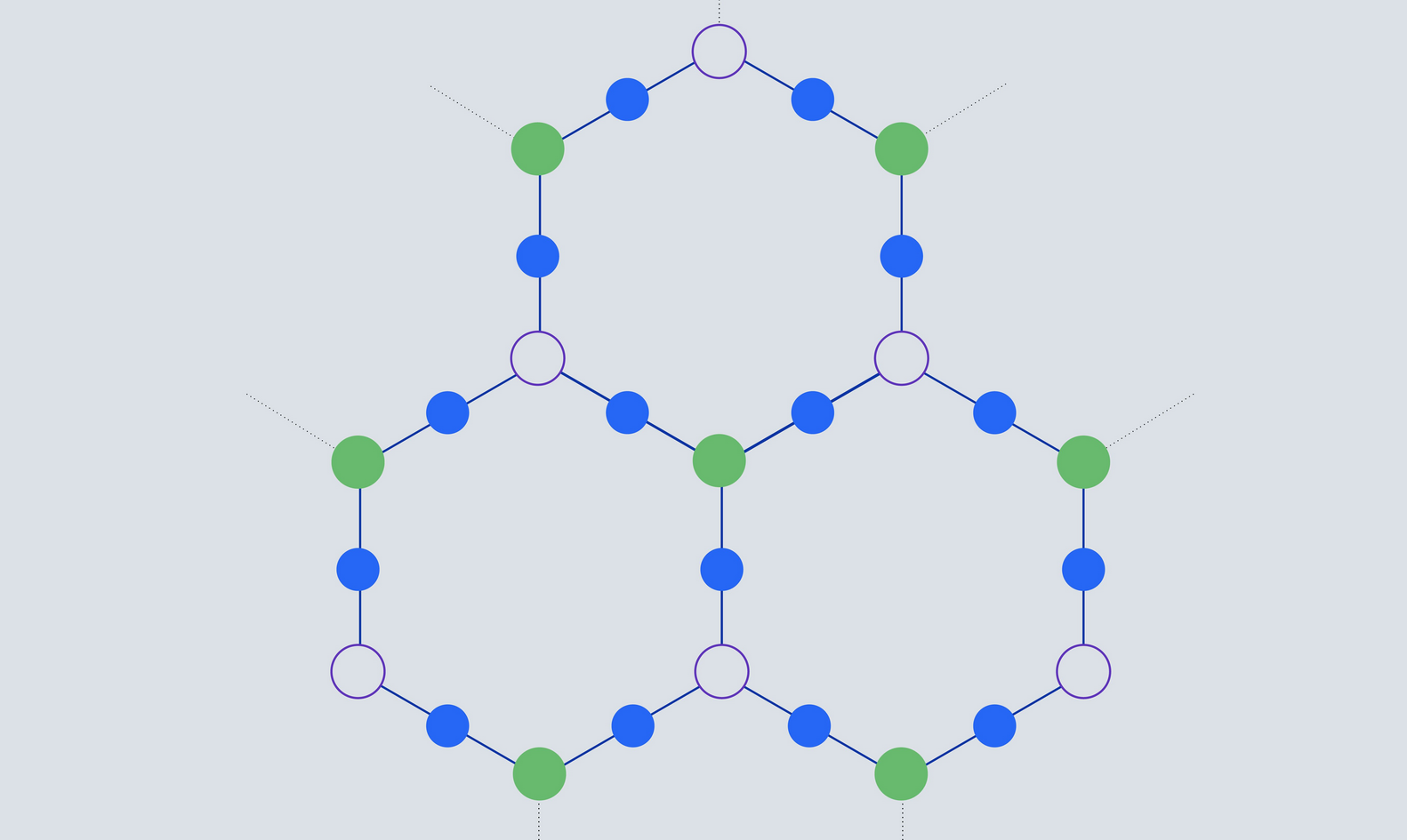

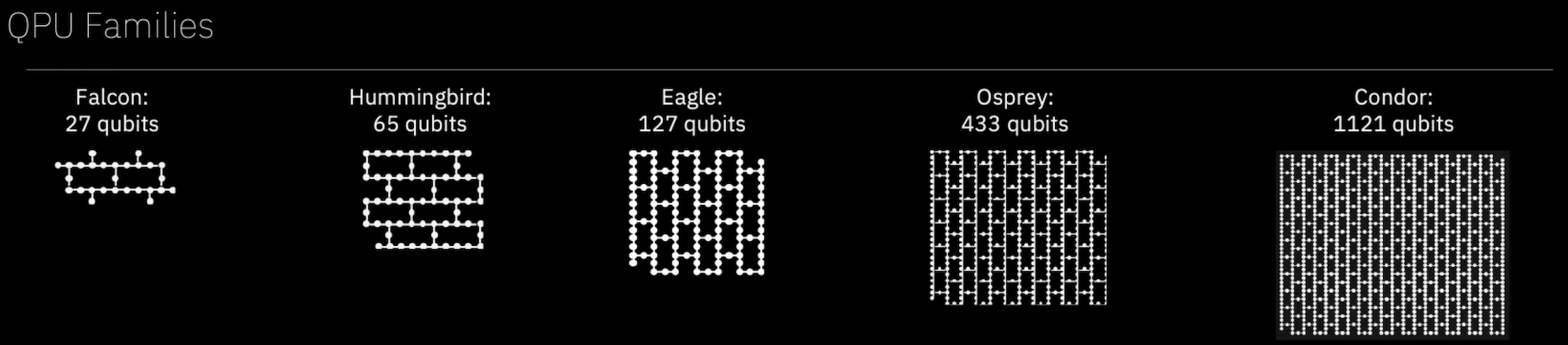

Aun así, la conectividad de la topología de los qubits es, en el mejor de los casos, de cuatro vecinos más cercanos, como en el Sycamore de Google. IBM utiliza una conectividad de “heavy hex lattice” desde 2021 (ver Fig. 3.22). Esta, utilizando celdas unitarias hexagonales de 12 qubits con conectividad 1 a 2 y 1 a 3, genera mejores fidelidades de puerta de qubit y permite la implementación de códigos de corrección de errores. Podemos ver varios chips con esta conectividad en la Fig. 3.23

Fig. 3.22 Topología “heavy hex lattice”#

Fig. 3.23 Topología de red para diferentes chips de IBM donde se usa la “heavy hex lattice”.#

Un nuevo enfoque consiste en utilizar chipsets de conectividad de múltiples capas que se conectan al chipset de qubits con conectores verticales TSV (through-silicon vias). Los diseños más recientes de IBM y los laboratorios Lincoln del MIT tienen entre tres y siete capas metálicas.

Nota (Los proceadores Falcon y Humminbird de IBM)

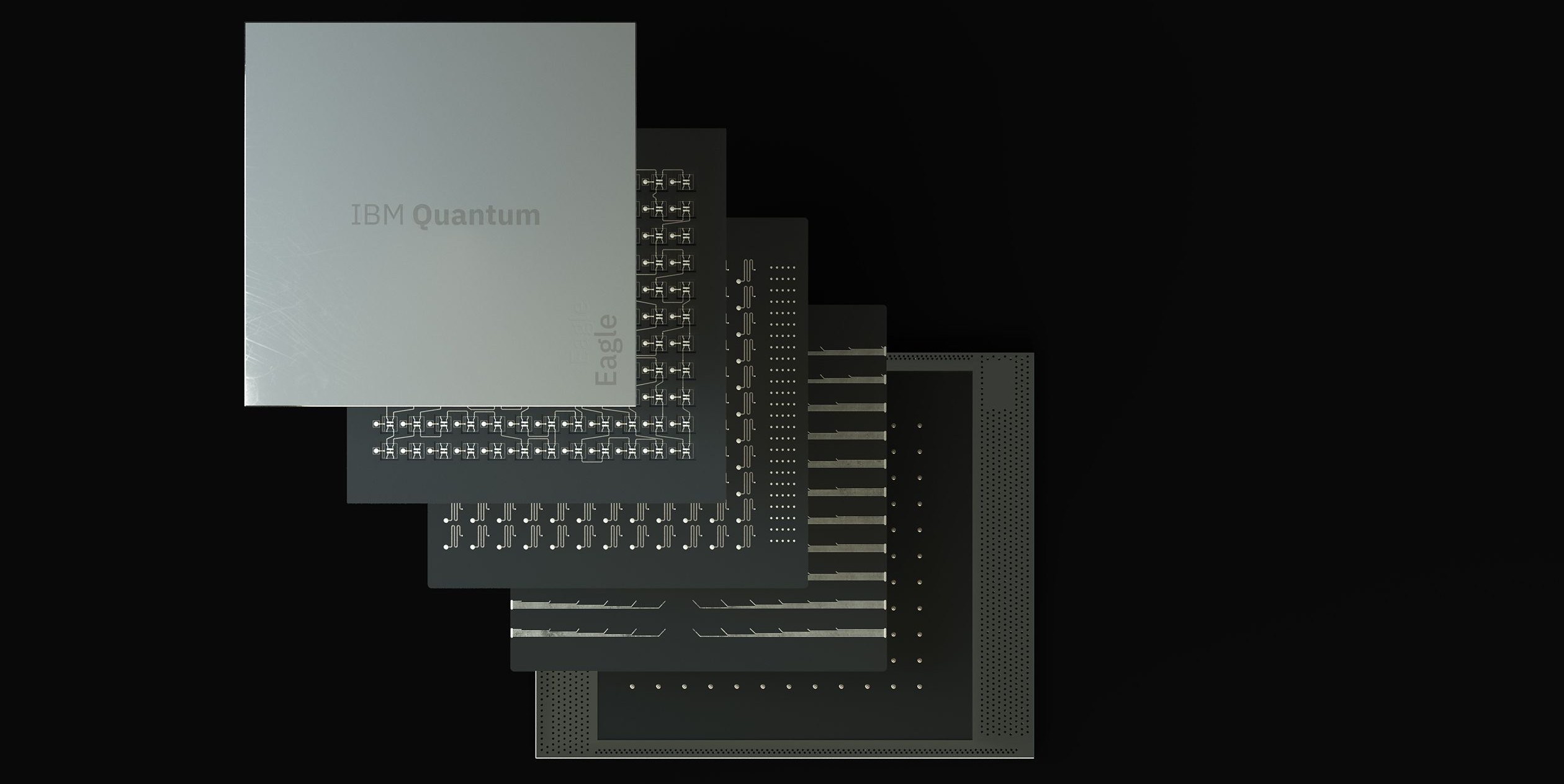

IBM utilizó por primera vez este tipo de arquitectura multicapa en el procesador Eagle de 127 qubits (ver Fig 3.25). Para el procesador Eagle, como antes, se usó una oblea de qubits unida a una oblea intercalada. Sin embargo, en este procesador se añadió un cableado multicapa (MLW, de sus siglas en inglés) dentro del intercalador. Las señales de control y lectura se dirigen en esta capa adicional, que está bien aislada del propio dispositivo cuántico y permite enviar señales a gran profundidad en chips de gran tamaño. El nivel MLW consta de tres capas metálicas, un dieléctrico planarizado entre cada nivel y unas conexiones cortas llamadas vías que conectan los niveles metálicos. Juntos, estos niveles permiten crear líneas de transmisión totalmente aisladas entre sí y del dispositivo cuántico. También se añadieron vías a través del sustrato a los chips de qubits e intercalador.

Fig. 3.24 Arquitecturas con una, dos y varias capas de chips de IBM.#

Fig. 3.25 Procesador Eagle de 127 qubits de IBM#

Autor:

David Castaño (UMA-SCBI)

License: Licencia Creative Commons Atribución-CompartirIgual 4.0 Internacional.

This work has been financially supported by the Ministry for Digital Transformation and of Civil Service of the Spanish Government through the QUANTUM ENIA project call - Quantum Spain project, and by the European Union through the Recovery, Transformation and Resilience Plan - NextGenerationEU within the framework of the Digital Spain 2026 Agenda.